- Our Story

- Publications & Resources

- Publications & Resources

- Publications

- IEEE Signal Processing Magazine

- IEEE Journal of Selected Topics in Signal Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Computational Imaging

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Signal and Information Processing over Networks

- IEEE Transactions on Signal Processing

- IEEE TCI

- IEEE TSIPN

- Data & Challenges

- Submit Manuscript

- Guidelines

- Information for Authors

- Special Issue Deadlines

- Overview Articles

- Top Accessed Articles

- SPS Newsletter

- SigPort

- SPS Resource Center

- Publications FAQ

- Blog

- News

- Dataset Papers

- Conferences & Events

- Community & Involvement

- Professional Development

- For Volunteers

- Information for Authors-OJSP

-

Home

ICASSP@50: A Recap [Conference Highlights]

Conversational Agents in the Era of Large Language Models

Conferences Events IEEE Signal Processing Magazine IEEE SPL Article IEEE TIFS Article IEEE TMM Article IEEE TSP Article Jobs in Signal Processing Lectures Machine Learning Seasonal Schools Signal Processing News SPM Article SPS Distinguished Lectures SPS Newsletter Article SPS Webinar SPS Webinars SPS Webinar Series Webinar webinars -

Our Story

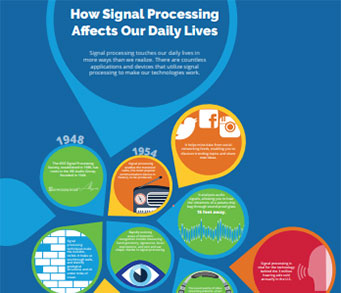

What is Signal Processing?

The technology we use, and even rely on, in our everyday lives –computers, radios, video, cell phones – is enabled by signal processing. Learn More » -

Publications & Resources

-

SPS Resources

- Signal Processing Magazine The premier publication of the society.

- SPS Newsletter Monthly updates in Signal Processing

- SPS Resource Center Online library of tutorials, lectures, and presentations.

- SigPort Online repository for reports, papers, and more.

- SPS Feed The latest news, events, and more from the world of Signal Processing.

-

SPS Resources

-

Conferences & Events

-

Community & Involvement

-

Membership

- Join SPS The IEEE Signal Processing Magazine, Conference, Discounts, Awards, Collaborations, and more!

- Chapter Locator Find your local chapter and connect with fellow industry professionals, academics and students

- Women in Signal Processing Networking and engagement opportunities for women across signal processing disciplines

- Students Scholarships, conference discounts, travel grants, SP Cup, VIP Cup, 5-MICC

- Young Professionals Career development opportunities, networking

- Get Involved

-

Technical Committees

- Applied Signal Processing Systems

- Audio and Acoustic Signal Processing

- Bio Imaging and Signal Processing

- Computational Imaging

- Image Video and Multidimensional Signal Processing

- Information Forensics and Security

- Machine Learning for Signal Processing

- Multimedia Signal Processing

- Sensor Array and Multichannel

- Signal Processing for Communication and Networking

- Signal Processing Theory and Methods

- Speech and Language Processing

- Technical Working Groups

- More TC Resources

-

Membership

-

Professional Development

-

Professional Development

- Signal Processing Mentorship Academy (SigMA) Program

- Micro Mentoring Experience Program (MiME)

- Distinguished Lecturer Program

- Distinguished Lecturers

- Distinguished Lecturer Nominations

- Past Lecturers

- Distinguished Industry Speaker Program

- Distinguished Industry Speakers

- Distinguished Industry Speaker Nominations

- Industry Resources

- IEEE Training Materials

- Jobs in Signal Processing: IEEE Job Site

-

Career Resources

- SPS Education Program Educational content in signal processing and related fields.

- Distinguished Lecturer Program Chapters have access to educators and authors in the fields of Signal Processing

- Job Opportunities Signal Processing and Technical Committee specific job opportunities

- Job Submission Form Employers may submit opportunities in the area of Signal Processing.

-

Professional Development

-

For Volunteers

-

For Board & Committee Members

- Board Agenda/Minutes* Agendas, minutes and supporting documentation for Board and Committee Members

- SPS Directory* Directory of volunteers, society and division directory for Board and Committee Members.

- Membership Development Reports* Insight into the Society’s month-over-month and year-over-year growths and declines for Board and Committee Members

-

For Board & Committee Members

Popular Pages

Today's:

- Information for Authors

- ICASSP@50: A Recap [Conference Highlights]

- (ICME 2026) 2026 IEEE International Conference on Multimedia and Expo

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- Conference Call for Papers

- IEEE Transactions on Image Processing

- Building Bridges for Our Professional Future [President’s Message]

- Signal Processing Cup

- Information for Authors-SPL

- IEEE JSTSP Special Issue on Advanced AI and Signal Processing for Low-Altitude Wireless Networks

- IEEE Signal Processing Letters

- (ASRU 2025) 2025 IEEE Automatic Speech Recognition and Understanding Workshop

- (CAI 2026) IEEE Conference on Artificial Intelligence 2026

- Submit a Manuscript

All time:

- Information for Authors

- Submit a Manuscript

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Audio, Speech and Language Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Signal Processing

- Conferences & Events

- IEEE Journal of Selected Topics in Signal Processing

- Information for Authors-SPL

- Conference Call for Papers

- Signal Processing 101

- IEEE Signal Processing Magazine

- Guidelines

Last viewed:

- SA-TWG Webinar: Channel Estimation for Beyond Diagonal RIS via Tensor Decomposition

- (CAI 2025) 2025 IEEE Conference on Artificial Intelligence

- IEEE Transactions on Signal Processing

- Shoji Makino

- Community & Involvement

- Scaling and Scalability: Accelerating Ill-conditioned Low-rank Estimation via Scaled Gradient Descent

- IEEE Open Journal of Signal Processing

- Guidelines for Reviewers

- Automatic Renewal Now Available for IEEE Membership

- Technical Liaison Committee/Editorial Board

- Information for Authors

- (ASRU 2025) 2025 IEEE Automatic Speech Recognition and Understanding Workshop

- PhD Studentship in Immersive Audio Technology

- ICASSP@50: A Recap [Conference Highlights]

- IEEE JSTSP Special Issue on Advanced AI and Signal Processing for Low-Altitude Wireless Networks

Resilient System-on-Chip Designs With NoC Fabrics

You are here

Transactions on Information Forensics and Security

Publications & Resources

For Authors

Top Reasons to Join SPS Today!

1. IEEE Signal Processing Magazine

2. Signal Processing Digital Library*

3. Inside Signal Processing Newsletter

4. SPS Resource Center

5. Career advancement & recognition

6. Discounts on conferences and publications

7. Professional networking

8. Communities for students, young professionals, and women

9. Volunteer opportunities

10. Coming soon! PDH/CEU credits

Click here to learn more.

Resilient System-on-Chip Designs With NoC Fabrics

Modern System-on-Chip (SoC) designs integrate a number of third party IPs (3PIPs) that coordinate and communicate through a Network-on-Chip (NoC) fabric to realize system functionality. An important class of SoC security attack involves a rogue IP tampering with the inter-IP communication. These attacks include message snoop, message mutation, message misdirection, IP masquerade, and message flooding. Static IP-level trust verification cannot protect against these SoC-level attacks. In this paper, we analyze the vulnerabilities of system level communication among IPs and develop a novel SoC security architecture that provides system resilience against exploitation by untrusted 3PIPs integrated over an NoC fabric. We show how to address the problem through a collection of fine-grained SoC security policies that enable on-the-fly monitoring and control of appropriate security-relevant events. Our approach, for the first time to our knowledge, provides an architecture-level solution for trusted SoC communication through run-time resilience in the presence of untrusted IPs. We demonstrate viability of our approach on a realistic SoC design through a series of attack models and show that our architecture incurs minimal to modest overhead in area, power, and system latency.

SPS Social Media

- IEEE SPS Facebook Page https://www.facebook.com/ieeeSPS

- IEEE SPS X Page https://x.com/IEEEsps

- IEEE SPS Instagram Page https://www.instagram.com/ieeesps/?hl=en

- IEEE SPS LinkedIn Page https://www.linkedin.com/company/ieeesps/

- IEEE SPS YouTube Channel https://www.youtube.com/ieeeSPS

Home | Sitemap | Contact | Accessibility | Nondiscrimination Policy | IEEE Ethics Reporting | IEEE Privacy Policy | Terms | Feedback

© Copyright 2025 IEEE - All rights reserved. Use of this website signifies your agreement to the IEEE Terms and Conditions.

A public charity, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity.