- Our Story

- Publications & Resources

- Publications & Resources

- Publications

- IEEE Signal Processing Magazine

- IEEE Journal of Selected Topics in Signal Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Computational Imaging

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Signal and Information Processing over Networks

- IEEE Transactions on Signal Processing

- IEEE TCI

- IEEE TSIPN

- Data & Challenges

- Submit Manuscript

- Guidelines

- Information for Authors

- Special Issue Deadlines

- Overview Articles

- Top Accessed Articles

- SPS Newsletter

- SigPort

- SPS Resource Center

- Publications FAQ

- Blog

- News

- Dataset Papers

- Conferences & Events

- Community & Involvement

- Professional Development

- For Volunteers

- Information for Authors-OJSP

-

Home

Conferences Events IEEE Signal Processing Magazine IEEE SPL Article IEEE TIFS Article IEEE TMM Article IEEE TSP Article Jobs in Signal Processing Lectures Machine Learning Seasonal Schools Signal Processing News SPM Article SPS Distinguished Lectures SPS Newsletter Article SPS Webinar SPS Webinars SPS Webinar Series Webinar webinars

-

Our Story

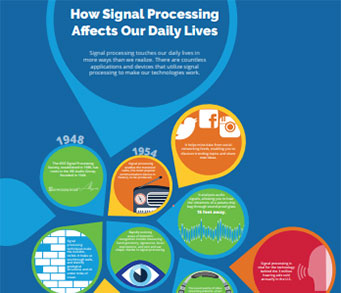

What is Signal Processing?

The technology we use, and even rely on, in our everyday lives –computers, radios, video, cell phones – is enabled by signal processing. Learn More » -

Publications & Resources

-

SPS Resources

- Signal Processing Magazine The premier publication of the society.

- SPS Newsletter Monthly updates in Signal Processing

- SPS Resource Center Online library of tutorials, lectures, and presentations.

- SigPort Online repository for reports, papers, and more.

- SPS Feed The latest news, events, and more from the world of Signal Processing.

-

SPS Resources

-

Conferences & Events

-

Community & Involvement

-

Membership

- Join SPS The IEEE Signal Processing Magazine, Conference, Discounts, Awards, Collaborations, and more!

- Chapter Locator Find your local chapter and connect with fellow industry professionals, academics and students

- Women in Signal Processing Networking and engagement opportunities for women across signal processing disciplines

- Students Scholarships, conference discounts, travel grants, SP Cup, VIP Cup, 5-MICC

- Young Professionals Career development opportunities, networking

- Get Involved

-

Technical Committees

- Applied Signal Processing Systems

- Audio and Acoustic Signal Processing

- Bio Imaging and Signal Processing

- Computational Imaging

- Image Video and Multidimensional Signal Processing

- Information Forensics and Security

- Machine Learning for Signal Processing

- Multimedia Signal Processing

- Sensor Array and Multichannel

- Signal Processing for Communication and Networking

- Signal Processing Theory and Methods

- Speech and Language Processing

- Technical Working Groups

- More TC Resources

-

Membership

-

Professional Development

-

Professional Development

- Signal Processing Mentorship Academy (SigMA) Program

- Micro Mentoring Experience Program (MiME)

- Distinguished Lecturer Program

- Distinguished Lecturers

- Distinguished Lecturer Nominations

- Past Lecturers

- Distinguished Industry Speaker Program

- Distinguished Industry Speakers

- Distinguished Industry Speaker Nominations

- Industry Resources

- IEEE Training Materials

- Jobs in Signal Processing: IEEE Job Site

-

Career Resources

- SPS Education Program Educational content in signal processing and related fields.

- Distinguished Lecturer Program Chapters have access to educators and authors in the fields of Signal Processing

- Job Opportunities Signal Processing and Technical Committee specific job opportunities

- Job Submission Form Employers may submit opportunities in the area of Signal Processing.

-

Professional Development

-

For Volunteers

-

For Board & Committee Members

- Board Agenda/Minutes* Agendas, minutes and supporting documentation for Board and Committee Members

- SPS Directory* Directory of volunteers, society and division directory for Board and Committee Members.

- Membership Development Reports* Insight into the Society’s month-over-month and year-over-year growths and declines for Board and Committee Members

-

For Board & Committee Members

Popular Pages

Today's:

- Information for Authors

- (ISBI 2026) 2026 IEEE 23rd International Symposium on Biomedical Imaging

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Image Processing

- (SPAWC 2025) 2025 IEEE Workshop on Signal Processing and Artificial Intelligence for Wireless Communications

- IEEE JSTSP Special Series on Artificial Intelligence for Smart Agriculture

- SPS Travel Grants

- IEEE Journal of Selected Topics in Signal Processing

- (ASRU 2025) 2025 IEEE Automatic Speech Recognition and Understanding Workshop

- Information for Authors-SPL

- (ICME 2026) 2026 IEEE International Conference on Multimedia and Expo

- IEEE Transactions on Audio, Speech and Language Processing

- Submit a Manuscript

- IEEE Transactions on Signal Processing

All time:

- Information for Authors

- Submit a Manuscript

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Audio, Speech and Language Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Signal Processing

- Conferences & Events

- IEEE Journal of Selected Topics in Signal Processing

- Information for Authors-SPL

- Conference Call for Papers

- Signal Processing 101

- IEEE Signal Processing Magazine

- Guidelines

Last viewed:

- IEEE Transactions on Signal Processing

- Call for Nominations for the SPS Chapter of the Year Award

- Guidelines for Reviewers

- Conference Resources

- IEEE Transactions on Information Forensics and Security

- Editorial Board Nominations

- Editorial Board

- (MMSP 2025) 2025 IEEE 26th International Workshop on Multimedia Signal Processing

- Call for Papers for IEEE JSTSP Special Series on Artificial Intelligence for Smart Agriculture

- Reviewer Instructions for OJSP Reproducibility Reviews

- About Transactions on Information Forensics and Security

- IEEE Open Journal of Signal Processing

- IEEE Transactions on Multimedia

- Conferences

- IEEE Transactions on Audio, Speech and Language Processing

Shi, Feng. (Lehigh University) “Signal processing techniques and applications” (2015)

You are here

Newsletter Menu

Newsletter Categories

Top Reasons to Join SPS Today!

1. IEEE Signal Processing Magazine

2. Signal Processing Digital Library*

3. Inside Signal Processing Newsletter

4. SPS Resource Center

5. Career advancement & recognition

6. Discounts on conferences and publications

7. Professional networking

8. Communities for students, young professionals, and women

9. Volunteer opportunities

10. Coming soon! PDH/CEU credits

Click here to learn more.

News and Resources for Members of the IEEE Signal Processing Society

Shi, Feng. (Lehigh University) “Signal processing techniques and applications” (2015)

Shi, Feng. (Lehigh University) “Signal processing techniques and applications” (2015), Advisor: Yan, Zhiyuan

As the technologies scaling down, more transistors can be fabricated into the same area, which enables the integration of many components into the same substrate, referred to as system-on-chip (SoC). The components on SoC are connected by on-chip global interconnects. It has been shown in the recent International Technology Roadmap of Semiconductors (ITRS) that when scaling down, gate delay decreases, but global interconnect delay increases due to crosstalk. The interconnect delay has become a bottleneck of the overall system performance. Many techniques have been proposed to address crosstalk, such as shielding, buffer insertion, and crosstalk avoidance codes (CACs). The CAC is a promising technique due to its good crosstalk reduction, less power consumption and lower area. In this dissertation, I will present analytical delay models for on-chip interconnects with improved accuracy. This enables us to have a more accurate control of delays for transition patterns and lead to a more efficient CAC, whose worst-case delay is 30-40% smaller than the best of previously proposed CACs. As the clock frequency approaches multi-gigahertz, the parasitic inductance of on-chip interconnects has become significant and its detrimental effects, including increased delay, voltage overshoots and undershoots, and increased crosstalk noise, cannot be ignored. The author introduces new CACs to address both capacitive and inductive couplings simultaneously.

Quantum computers are more powerful in solving some NP problems than the classical computers. However, quantum computers suffer greatly from unwanted interactions with environment. Quantum error correction codes (QECCs) are needed to protect quantum information against noise and decoherence. Given their good error-correcting performance, it is desirable to adapt existing iterative decoding algorithms of LDPC codes to obtain LDPC-based QECCs. Several QECCs based on nonbinary LDPC codes have been proposed with a much better error-correcting performance than existing quantum codes over a qubit channel. In this dissertation, I will present stabilizer codes based on nonbinary QC-LDPC codes for qubit channels. The results will confirm the observation that QECCs based on nonbinary LDPC codes appear to achieve better performance than QECCs based on binary LDPC codes.

As the technologies scaling down further to nanoscale, CMOS devices suffer greatly from the quantum mechanical effects. Some emerging nano devices, such as resonant tunneling diodes (RTDs), quantum cellular automata (QCA), and single electron transistors (SETs), have no such issues and are promising candidates to replace the traditional CMOS devices. Threshold gate, which can implement complex Boolean functions within a single gate, can be easily realized with these devices. Several applications dealing with real-valued signals have already been realized using nanotechnology based threshold gates. Unfortunately, the applications using finite fields, such as error correcting coding and cryptography, have not been realized using nanotechnology. The main obstacle is that they require a great number of exclusive-ORs (XORs), which cannot be realized in a single threshold gate. Besides, the fan-in of a threshold gate in RTD nanotechnology needs to be bounded for both reliability and performance purpose. In this dissertation, I will present a majority-class threshold architecture of XORs with bounded fan-in, and compare it with a Boolean-class architecture. I will show an application of the proposed XORs for the finite field multiplications. The analysis results will show that the majority class outperforms the Boolean class architectures in terms of hardware complexity and latency. I will also introduce a sort-and-search algorithm, which can be used for implementations of any symmetric functions. Since XOR is a special symmetric function, it can be implemented via the sort-and-search algorithm. To leverage the power of multi-input threshold functions, I generalize the previously proposed sort-and-search algorithm from a fan-in of two to arbitrary fan-ins, and propose an architecture of multi-input XORs with bounded fan-ins.

For details, please visit the thesis page.

Open Calls

Publications News

Society News

- IEEE Signal Processing Society participates in NextBC 2 Showcase and Awards Gala

- 22 Signal Processing Society Members Elevated to Senior Member

- Women in Signal Processing LinkedIn Group

- Call for Nominations: Chapter of the Year Award

- Nominations Open for 2015 Major SPS Awards

- IEEE-USA Offers Free e-books to Members in May and June

- Get Involved in IEEE Future Directions Initiatives

- Help Conference Authors Meet Open Access Publishing Requirements

- IEEE Meetings, Conferences & Events (MCE) Conference Education Program Webinars

- Call for Proposals: IEEE SIGHT Project Funding in 2015

- Member Discounts: Learn About Risk Management

- Call for Grant Applications: IEEE Foundation/IEEE Life Members Fund: Deadline 1 August

- Volunteers Needed for IEEE Awards

- Call for Nominations: IEEE Medals and Recognitions: Deadline 1 July

- Member Discounts: Mobile Property Insurance for Regions 8-10

- Call for Nominations: Chapters Committee Chair, Education Committee Chair and Seasonal Schools Subcommittee Chair

- Use vTools.Meetings for More than Just Submitting Reports

- Welcome New Members in your Section and Invite them to Attend an Orientation Webinar

Technical Committee News

Education & Resources

SPS Social Media

- IEEE SPS Facebook Page https://www.facebook.com/ieeeSPS

- IEEE SPS X Page https://x.com/IEEEsps

- IEEE SPS Instagram Page https://www.instagram.com/ieeesps/?hl=en

- IEEE SPS LinkedIn Page https://www.linkedin.com/company/ieeesps/

- IEEE SPS YouTube Channel https://www.youtube.com/ieeeSPS

Home | Sitemap | Contact | Accessibility | Nondiscrimination Policy | IEEE Ethics Reporting | IEEE Privacy Policy | Terms | Feedback

© Copyright 2025 IEEE - All rights reserved. Use of this website signifies your agreement to the IEEE Terms and Conditions.

A public charity, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity.