- Our Story

- Publications & Resources

- Publications & Resources

- Publications

- IEEE Signal Processing Magazine

- IEEE Journal of Selected Topics in Signal Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Computational Imaging

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Signal and Information Processing over Networks

- IEEE Transactions on Signal Processing

- IEEE TCI

- IEEE TSIPN

- Data & Challenges

- Submit Manuscript

- Guidelines

- Information for Authors

- Special Issue Deadlines

- Overview Articles

- Top Accessed Articles

- SPS Newsletter

- SigPort

- SPS Resource Center

- Publications FAQ

- Blog

- News

- Dataset Papers

- Conferences & Events

- Community & Involvement

- Professional Development

- For Volunteers

- Information for Authors-OJSP

-

Home

Conferences Events IEEE Signal Processing Magazine IEEE SPL Article IEEE TIFS Article IEEE TMM Article IEEE TSP Article Jobs in Signal Processing Lectures Machine Learning Seasonal Schools Signal Processing News SPM Article SPS Distinguished Lectures SPS Newsletter Article SPS Webinar SPS Webinars SPS Webinar Series Webinar webinars

-

Our Story

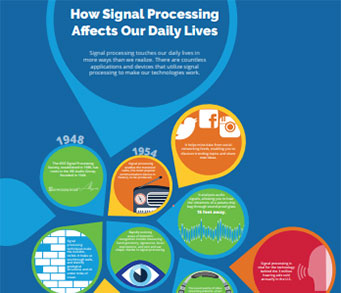

What is Signal Processing?

The technology we use, and even rely on, in our everyday lives –computers, radios, video, cell phones – is enabled by signal processing. Learn More » -

Publications & Resources

-

SPS Resources

- Signal Processing Magazine The premier publication of the society.

- SPS Newsletter Monthly updates in Signal Processing

- SPS Resource Center Online library of tutorials, lectures, and presentations.

- SigPort Online repository for reports, papers, and more.

- SPS Feed The latest news, events, and more from the world of Signal Processing.

-

SPS Resources

-

Conferences & Events

-

Community & Involvement

-

Membership

- Join SPS The IEEE Signal Processing Magazine, Conference, Discounts, Awards, Collaborations, and more!

- Chapter Locator Find your local chapter and connect with fellow industry professionals, academics and students

- Women in Signal Processing Networking and engagement opportunities for women across signal processing disciplines

- Students Scholarships, conference discounts, travel grants, SP Cup, VIP Cup, 5-MICC

- Young Professionals Career development opportunities, networking

- Get Involved

-

Technical Committees

- Applied Signal Processing Systems

- Audio and Acoustic Signal Processing

- Bio Imaging and Signal Processing

- Computational Imaging

- Image Video and Multidimensional Signal Processing

- Information Forensics and Security

- Machine Learning for Signal Processing

- Multimedia Signal Processing

- Sensor Array and Multichannel

- Signal Processing for Communication and Networking

- Signal Processing Theory and Methods

- Speech and Language Processing

- Technical Working Groups

- More TC Resources

-

Membership

-

Professional Development

-

Professional Development

- Signal Processing Mentorship Academy (SigMA) Program

- Micro Mentoring Experience Program (MiME)

- Distinguished Lecturer Program

- Distinguished Lecturers

- Distinguished Lecturer Nominations

- Past Lecturers

- Distinguished Industry Speaker Program

- Distinguished Industry Speakers

- Distinguished Industry Speaker Nominations

- Industry Resources

- IEEE Training Materials

- Jobs in Signal Processing: IEEE Job Site

-

Career Resources

- SPS Education Program Educational content in signal processing and related fields.

- Distinguished Lecturer Program Chapters have access to educators and authors in the fields of Signal Processing

- Job Opportunities Signal Processing and Technical Committee specific job opportunities

- Job Submission Form Employers may submit opportunities in the area of Signal Processing.

-

Professional Development

-

For Volunteers

-

For Board & Committee Members

- Board Agenda/Minutes* Agendas, minutes and supporting documentation for Board and Committee Members

- SPS Directory* Directory of volunteers, society and division directory for Board and Committee Members.

- Membership Development Reports* Insight into the Society’s month-over-month and year-over-year growths and declines for Board and Committee Members

-

For Board & Committee Members

Popular Pages

Today's:

- Information for Authors

- (ICME 2026) 2026 IEEE International Conference on Multimedia and Expo

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- 2025 IEEE SPS Chapter Initiative: SPECTRE (Signal Processing Expo and Creatathon for Technical Research and Excellence)

- Information for Authors-SPL

- Conference Call for Papers

- IEEE Transactions on Image Processing

- IEEE Transactions on Signal Processing

- IEEE Signal Processing Letters

- Submit a Manuscript

- 2025 IEEE SPS Chapter Initiative: S.P.A.R.C. – Signal Processing, AI & Real-time Computing Camp

- IEEE Journal of Selected Topics in Signal Processing

- Unified EDICS

- Guidelines

All time:

- Information for Authors

- Submit a Manuscript

- IEEE Transactions on Image Processing

- IEEE Transactions on Information Forensics and Security

- IEEE Transactions on Multimedia

- IEEE Transactions on Audio, Speech and Language Processing

- IEEE Signal Processing Letters

- IEEE Transactions on Signal Processing

- Conferences & Events

- IEEE Journal of Selected Topics in Signal Processing

- Information for Authors-SPL

- Conference Call for Papers

- Signal Processing 101

- IEEE Signal Processing Magazine

- Guidelines

Last viewed:

- Editorial Board

- Information for Authors

- IEEE Transactions on Multimedia

- Updated SPS Chapter Logo Usage and Branding Guidelines

- Conferences & Events

- Hyderabad Chapter

- Guidelines for Associate Editors

- (ICME 2026) 2026 IEEE International Conference on Multimedia and Expo

- Integrated Sensing and Communication Technical Working Group

- Access Restricted

- IEEE Transactions on Audio, Speech and Language Processing

- IEEE Transactions on Information Forensics and Security

- 2025 International Conference on Quality of Multimedia Experience (QoMEX)

- SPS Branding Materials

- (ISBI 2026) 2026 IEEE 23rd International Symposium on Biomedical Imaging

Kong, Long, (University of California, Los Angeles), “RF Synthesis without Inductors” (2016)

You are here

Newsletter Menu

Newsletter Categories

Top Reasons to Join SPS Today!

1. IEEE Signal Processing Magazine

2. Signal Processing Digital Library*

3. Inside Signal Processing Newsletter

4. SPS Resource Center

5. Career advancement & recognition

6. Discounts on conferences and publications

7. Professional networking

8. Communities for students, young professionals, and women

9. Volunteer opportunities

10. Coming soon! PDH/CEU credits

Click here to learn more.

News and Resources for Members of the IEEE Signal Processing Society

Kong, Long, (University of California, Los Angeles), “RF Synthesis without Inductors” (2016)

Kong, Long, (University of California, Los Angeles), “RF Synthesis without Inductors” (2016) Advisor: Razavi, Behzad

Recent developments in RF receiver design have eliminated all on-chip inductors except for that used in the local oscillator. This dissertation addresses the “last inductor” problem and proposes both integer-N and fractional-N synthesizer architectures that achieve a phase noise and figure of merit (FOM) comparable to those of LC-VCO-based realizations.

A new wideband integer-N synthesizer is introduced to sufficiently suppress the ring’s phase noise. It employs an exclusive-OR (XOR) phase detector and a master-slave sampling filter (MSSF) to achieve a lock range of 2-3 GHz, a loop bandwidth equal to one half of the reference frequency, and a locked phase noise of -114 dBc/Hz up to 10-MHz offset with a 3-stage ring oscillator. Realized in 45-nm CMOS technology, the design uses a harmonic trap to suppress reference sidebands to less than -65 dBc while consuming 4 mW.

The wideband architecture has been successfully extended to a fractional-N loop as well. A ring-oscillator-based cascaded synthesizer incorporates a digital synchronous delay line and an analog noise trap to suppress the quantization noise of the Sigma-Delta modulator. Realized in 45-nm CMOS technology, the synthesizer exhibits an in-band phase noise of -109 dBc/Hz and an integrated rms jitter of 1.68 ps at 2.4 GHz with a power consumption of 6.4 mW.

Open Calls

| Nomination/Position | Deadline |

|---|---|

| Call for Nominations for the SPS Chapter of the Year Award | 15 October 2025 |

| Call for Papers for 2026 LRAC Workshop | 22 October 2025 |

| Submit Your 2026 ICASSP Workshop Paper | 22 October 2025 |

| Submit a Proposal for ICASSP 2030 | 31 October 2025 |

| Call for Project Proposals: IEEE SPS SigMA Program - Signal Processing Mentorship Academy | 2 November 2025 |

| Submit Your Proposals for 2026 Member-Driven Initiatives | 21 November 2025 |

| IEEE Signal Processing Society Annual Election Opens on 17 October | 4 December 2025 |

Society News

- GlobalSIP 2016: Call for Participation

- Featured News Around IEEE: IEEE Smart Grid Newsletter

- MGA Financial Reporting Deadline Changed to Last Day of February

- Call for Proposals: IEEE Humanitarian Activities Committee Project Funding in 2016: Deadline 15 September

- Invite Members in your Section to Attend an Orientation Webinar or New Ignite Information Session

- Get Involved in IEEE Future Directions Initiatives

- Announcing the New vTools.Events and Updates to vTools.eNotice

- Election of Regional Directors-at-Large and Members-at-Large

- Call for Nominations: N&A Committee and Awards Boards

- Start Planning for IEEE Day 2016 on 4 October

- Contests in Signal Processing and Machine Learning

- Upcoming Distinguished Lectures

- Do NOT Blindly Vote for the IEEE Constitutional Amendment

- 8 Signal Processing Society Members Elevated to Senior Member

Education & Resources

- IEEE-USA Offers Free e-Books to Members in August and September

- IEEE Women in Engineering News: Leadership Summits and Events

- IEEE Maker Project Competition: Deadline 17 September

- News from IEEE Educational Activities: New Courses Available on IEEEx.org, Publications from Standards Education and IEEE-HKN

- Recognize Outstanding Volunteers: Call for MGA Awards Nominations: Deadline 15 October

- Advance your Career with Mentoring and Employment Opportunities in IEEE Collabratec

- MIT Online Course 6.341x Discrete-Time Signal Processing is now free, online, interactive, and open to the world

Technical Committee News

Conferences & Events

SPS Social Media

- IEEE SPS Facebook Page https://www.facebook.com/ieeeSPS

- IEEE SPS X Page https://x.com/IEEEsps

- IEEE SPS Instagram Page https://www.instagram.com/ieeesps/?hl=en

- IEEE SPS LinkedIn Page https://www.linkedin.com/company/ieeesps/

- IEEE SPS YouTube Channel https://www.youtube.com/ieeeSPS

Home | Sitemap | Contact | Accessibility | Nondiscrimination Policy | IEEE Ethics Reporting | IEEE Privacy Policy | Terms | Feedback

© Copyright 2025 IEEE - All rights reserved. Use of this website signifies your agreement to the IEEE Terms and Conditions.

A public charity, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity.